¶ Interface Management Plan

¶ 1. Applicability Domain

The interface management plan shall be used for all interfaces in bewteen two different subsystems. Every interface type shall be managed independantly from each other, for example the data interface in bewteen AV and HY-B shall be treated independantly from the power interface inbetween AV and HY-B.

¶ 2. Management Logic

The goal of the interface plan is to prevent any potential interfacing problems by: identifying all interfaces, specifying requirements for each interface, defining and documenting the interface, communicating interface changes and creating a validation plan.

¶ 3. Change Management Approach

All changes shall be requested either on the dedicated slack channel or during a interface meeting.

All approved changes shall be logged in the dedicated section of the respective Low Level Interface Management document.

¶ 4. Timeline

All interfaces shall be identified before the PDR.

All interfaces data should not change after the CDR.

ALL interface verification tests shall be done by the end of the integrated tests.

¶ Types of Interfaces

¶ 1. Physical

Physical interfaces correspond to points where physical contact occurs, such as Bolts, Glued joints, Welds or Connectors. Physical interfaces are always symmetrical.

¶ 2. Mass

Mass interfaces correspond to points where mass flow occurs, such as Gas, Fluid or Solid transfer areas.

¶ 3. Energy

Energy interfaces correspond to points where energy transfer occurs, such as Electrical power, Thermal power, RF power or Mechanical power transfer.

¶ 4. Information

Information interfaces correspond to points where information flow occurs, such as User-GUI, Sensor-Host boards or Antenna-Antenna communication.

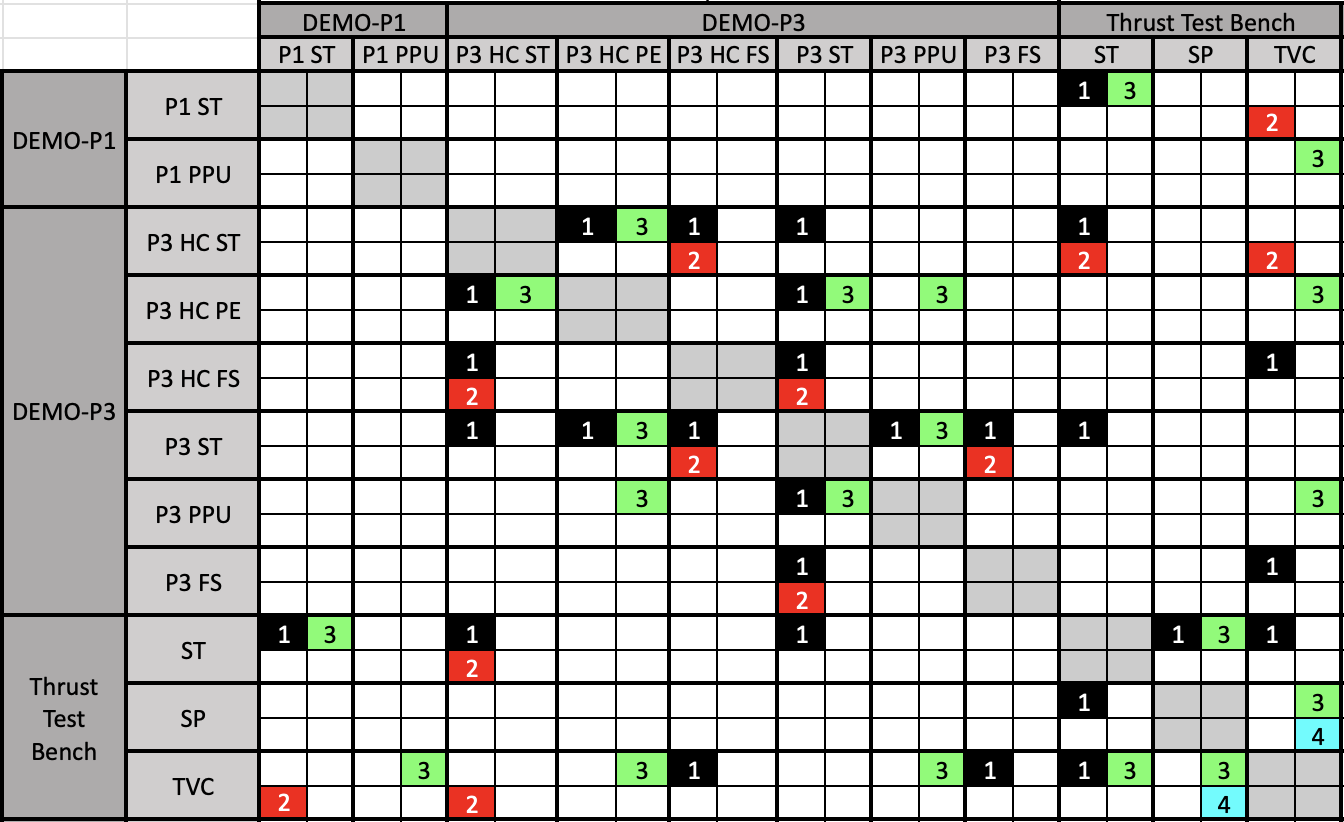

¶ Design Structure Matrix

Design Structure Matrix (DSM, also known as Dependency and Structure Modelling) techniques support the management of complexity by focusing attention on the elements of a complex system and how they relate to each other[reference].

The DSM highlights how the different subsystems/assemblies/subassemblies/parts interface with each other in order to better sythesize and manage interfaces.

To read the DSM, please refer to the following legend:

To Fill

¶ Block Diagrams

¶ Demo-P1: Thrust Test Setup

¶ Demo-P3

To Fill

¶ Interfaces

¶ Intra-subsytem Interfaces

¶ DEMO-P1

¶ DEMO-P2

¶ DEMO-P3

¶ Extra-subsytem Interfaces

Interfaces nomenclature (in case of extra-subsytem interfaces): 2024_H_PC_PX_PY_LLIM (symmetric)